# Strombelastbarkeit von Layouts – Design, Simulation und Messung Current Carrying Capacity of Layouts – Design, Simulation and Experiment

Dr. Johannes Adam, ADAM Research, Theodor-Heuss-Str. 12, D-69181 Leimen, Germany

Marc Mitchell, Robert Bosch GmbH, Robert-Bosch-Str. 2, D-71701 Schwieberdingen, Germany

## Kurzfassung

Leiterplatten im Automotive-Bereich und in der Leistungselektronik müssen hohe Ströme transportieren, wobei die Temperatur einen Schwellenwert nicht überschreiten darf. Die genauere Betrachtung von Schaltungen auf Multilayerboards führt aber schnell zu einer komplexen dreidimensionalen Stromheizung und zu entsprechenden Wechselwirkungen im Wärmetransport. Daher können sowohl die alte Richtlinie ICP-2221 als auch die neue IPC-2152 nur sehr grobe und spezielle Anhaltspunkte für einen maximalen Stromwert, bzw. die Leiterbahnparameter liefern. Um realistische Aussagen zu erhalten, berechnen wir detailliert durch die numerische Lösung der Potential- und Fouriergleichung, auf realistischen kompletten Layouts die Potentialverteilung (Spannungsabfall) den Stromfluss, die lokale Heizung und die Temperaturverteilung mit hoher Auflösung. Dabei wird auch der vertikale Transport berücksichtigt. Da die Ergebnisse einer neu eingeführten Simulationsmethode immer an realen Testobjekten überprüft werden, stellen wir auch Methode und Erfahrungen mit thermischer und elektrischer Messtechnik an Leiterplatten vor. Die thermischen und elektrischen Messergebnisse stimmen mit der Simulation im Rahmen einer Abweichung von 10% sehr gut überein. Letztendlich soll die Simulationsmethode erreichen, wie man neue Leiterplattenentwicklungen im Vorfeld effektiver, sicherer und kostengünstiger gestalten kann.

#### •

### **Abstract**

Printed circuit boards designed for automotive applications have to transport high currents which heat traces and board. In order not to overheat the board material, trace parameters could be estimated using design rules, such as IPC-2221 and IPC-2152. However, these describe very special and unrealistic situations. To get realistic predictions of the temperature field in 3D, including and based on the multilayer stack and the layout design of all layers, we perform numerical high-resolution simulations of electric potential, current and temperature. We describe first our experimental techniques and find that the calculated temperatures agree with in a margin of 10% very well with infrared thermography.

# 1 Einleitung und Motivation

An die Temperaturbelastbarkeit von Leiterplatten im Automotive-Bereich werden hohe Anforderungen gestellt. Vor allem die extremen Umgebungstemperaturen von 40 bis +140 °C, die Trends zum Downsizing und zur Erhöhung der Leistungsdichte erfordern neue technologische Ansätze. Zusätzlich fordern immer mehr elektrische Verbraucher im Fahrzeug und die Elektromobilität den Transport hoher Ströme bis 200 A über die Leiterbahnen, ohne dass die dadurch entstehende Stromheizung die Leiterplatte lokal über eine gesetzte Grenztemperatur erwärmt. Die Stromstärke, die die Grenztemperatur einhält nennt man *Strombelastbarkeit*. Insbesondere bei hohen Umgebungstemperaturen sind die Heizung durch Hochstromleiterbahnen und Bauteile und die Wärmespreizung durch das Layout gut aneinander anzupassen.

Eine klassische Methode Leiterbahnbreite und –dicke für ein bestimmtes Wertepaar von Stromstärke und Temperatur auszulegen geht über die alte Design Richtlinie in der IPC-2221 [1] und die neue IPC-2152 [2,3,4]. Würde man das Layout Design nach der IPC Norm auslegen, führte

dies entweder zu einem Unterdesign oder Überdesign. Der Grund dafür ist, dass beide Richtlinien relativ unrealistische Annahmen über den Boardaufbau und das Layout machen: nur eine geradlinige Leiterbahn, Board 2-lagig (IPC-2221) bzw. 1-lagig (IPC-2152) [5].

Die numerische Simulation des *kompletten 3D-Layouts* kann die Temperaturvorhersage genauer machen und Hinweise für Schwachstellen und Optimierung liefern. Um ein optimiertes Board Design (Aufbau und Layout) zu bekommen haben wir uns entschieden dies durch eine numerische Simulation abzusichern. Vor dem Routineeinsatz, ist aber eine experimentelle Überprüfung der Simulationsergebnisse ein notwendiges Muss.

## 2 Messung

Da Leiterplatten mit einem Bild mit vielen Mustern und Formen zu vergleichen sind, liegt es nahe die Oberflächentemperaturen mit einer Wärmebildkamera zu Vermessen. Die von uns verwendete Wärmebildkamera hat ein Mikrobolometer, eine Auflösung von 640x480 Pixel und eine thermische Empfindlichkeit von 80 mK bei 30

Hz. Somit sind kleinste Details zu erkennen. Die Thermokamera misst primär die vom Prüfling emittierte und reflektierte Strahlung und rechnet sie in eine Temperatur um. .Das größte Problem bei der Leiterplattenthermografie ist das kleine ΔT zur Umgebung. Wenn die Leiterbahnen z.B. nach einem ΔT=20 K ausgelegt werden, kann man sich leicht vorstellen, dass der Körper des Messenden mit ca. 37 °C einer der größten Störfaktoren bei der Messung ist, zumal wenn er sich direkt vor dem zu messenden Objekt aufhält. Daher sollte er sich bei einer Aufnahme möglichst kurzfristig davor aufhalten. Weiterhin werden alle anderen großen Wärmequellen wie Sonnenlicht und Heizkörper, die sich in unmittelbare Nähe befinden, sehr störend auf das messende Objekt einwirken. Aber nicht nur Quellen, sondern auch "Sichtkontakt" zu Wärmesenken, wie Fenster, Himmel und Klimaauslässe sind zu vermeiden.

#### 2.1 Die Feindbilder der Thermografie

Um ein richtiges Ergebnis zu bekommen, ist ein vernünftiger Messaufbau von größter Wichtigkeit (Bild 1).

**Bild 1** Beispiel für einen Messaufbau, um unerwünschte Nebeneffekt bei der Thermographie zu unterdrücken.

Weiterhin müssen wir die Leiterplatte gegen jeglichen Luftzug schützen. Schon eine kleine Luftbewegung von  $v_{Luft}=0.5$  m/s verfälscht das  $\Delta T$ -Ergebnis um bis zu 30%. Eine Maßnahme, wie in Bild 1 zu sehen, ist geeignet die Leiterplatte gegen Luftzug und Wärmestrahlung von außen zu schützen.

Große unlackierte Layoutflächen aus Lot oder Kupfer reflektieren die Umgebungsstrahlung, so dass man statt der Leiterplattentemperatur nur die Umgebungstemperatur sieht. Um diese Reflexion zu vermeiden, besprühen wir die Flächen mit Tetenal Schwarzlack und haben damit einen gleichmäßige Emissionsgrad von ε=0.94.

#### 2.2 Kabel

Die richtige Wahl der Kabel ist sowohl für die Thermik, als auch für die elektrische Messung wichtig. Die stromzuführenden Kabel dürfen nicht zu dünn sein, damit durch Eigenerwärmung keine zusätzliche Heizung in das Board eingebracht wird, aber auch nicht zu dick, so dass massiv Wärme über die Kontaktstelle aus dem Board abgeführt wird. In beiden Fällen wäre das Kabel als 'heiß' auf dem Wärmebild zu sehen. Am besten ist ein Temperaturgradient von Null, d.h. das Kabel erscheint so warm wie das Board.

Die Messung des Spannungsabfalls über eine Leiterbahn ist eine Kontrollmessung für die elektrischen Simulationsergebnisse. Hierbei muss ein unabhängiges zweites Paar von Messdrähten mit dünnen Messspitzen benutzt werden.

#### 3 Simulation

Die Leiterplatte sei ein rechteckiges x-y- Berechnungsgebiet mit vergleichsweise kleiner Dicke in z. Besonderheiten sind die sehr inhomogenen und sprunghaften Verteilungen der Wärmeleitfähigkeit  $\lambda(x_i,y_j,z_k)$  und der elektrischen Leitfähigkeit  $\sigma(x_i,y_j,z_k)$ . In und auf diesen Karten liegen Quellen und Senken für Wärme (Watt oder °C) und/oder Strom (Ampere oder Volt).

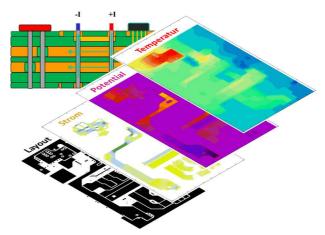

**Bild 2** Prinzipskizze zur Arbeitsweise der TRM-Software. Strom wird über Pins ein- und ausgeleitet und sind über das Layout miteinander verknüpft.

Nach der x-y Diskretisierung des Leiterbilds in allen Lagen und aller Bohrungen mit einer Auflösung der Größenordnung 0.1 mm bis 0.2 mm werden die el. Spannung  $U(x_i,y_j,z_k)$  aus der Potentialgleichung (Gleichstrom) und die  $Temperatur\ T(x_i,y_j,z_k)$  aus der partiellen Differentialgleichung der Wärmeleitung mit effektiven iterativen linearen Methoden gelöst. Die lokale Heizleistung ist  $\sigma |\nabla U|^2$ . Die Wärmeübertragung an die Umgebung geschieht durch Vorgabe von Umgebungstemperatur und

Wärmeübergangskoeffizient. Aus einem Dienstleistungsprojekt eines der Autoren (JA) wurde im letzten Jahr ein vertriebsfähiges Softwareprodukt, genannt *TRM 1.2* (Bild 2) [6]. Es ist in Eingabe und Menüführung speziell an den Bedarf von Leiterplattenlayoutern und Elektronikentwicklern zugeschnitten, der die Vorarbeiten in seinem gewohnten CAD Umfeld durchführt und Gerber-, CNC-Bohrdaten und Bestückungsdaten übergibt. Dabei ist er nicht auf die Verwendung von hochpreisigen Tools angewiesen. Es können aber auch Berechner ohne CAD Zugang die Simulationen aufsetzen und durchführen.

## **4 Vergleich Messung - Simulation**

#### 4.1 IPC-Testfälle

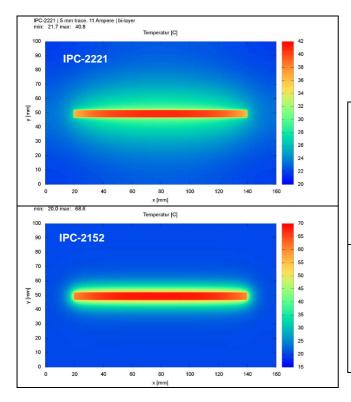

Für sehr spezielle Bedingungen zeigen die Designrichtlinien IPC-2221 [1] und IPC-2152 [2] den gemessenen Zusammenhang zwischen Strom und Temperaturerhöhung: eine einzige geradlinige Leiterbahn (Kupferdicke=35 μm) auf der Top-Seite ist unter Strom. Die Platte der IPC-2152 ist sogar nur einlagig, während die IPC-2221 Platte zweilagig mit einer kompletten Kupferlage auf Bottom ist. Diese Zusatzlage bewirkt eine bessere Wärmespreizung und führt dazu, dass die Leiterbahnen in der IPC-2221 kälter sind als in der IPC-2152, oder anders ausgedrückt: die Strombelastbarkeit ist nach IPC-2221 höher. Bild 3 zeigt das Simulationsergebnis für jeweils 5 mm (0.2 inch) Leiterbahnbreite (ergibt einen Leiterquerschnitt von 270 sq.mils bei 1 oz) und 11 A Strombelastung. Die Übereinstimmung mit den IPC-Werten ist sehr gut: an der  $\Delta T=20$ °C Kurve der IPC-2221 liest man ca. 11 A ab und für 11 A liefert die IPC-2152 ein ∆T≈50°C. Da die Temperaturen übereinstimmen, müssen es auch die Spannungen und Stromdichten tun.

**Bild 3** Boardtemperatur bei 11 A. oben: Aufbau nach IPC-2221 (ΔT=20K), unten: Aufbau nach IPC-2152 (ΔT=50 K). Simulation und IPC-Werte stimmen überein.

Diese speziellen Leiterplatten wurden vom IPC deshalb so gewählt, um Leiterbahnen möglichst *konservativ* auszulegen, so dass durch mehr Kupfer und Lagen es nur noch kälter = besser werden kann. Der Nachteil ist Verschwendung von Platz und Material.

#### 4.2 Layout-Testfälle

Gerade ausgerichtete und einzeln auftretende Leiterbahnen sind nicht realistisch. Deshalb wurde bei Bosch schon früher eine Reihe von Testleiterplatten verwirklicht und von einem der Autoren (MM) mit der Thermokamera untersucht. Einige von diesen wurden diesen neuen Simulationstests unterzogen. Weitere Simulationsbeispiele mit Platten, die bereits im Handel sind, zeigen wir in der mündlichen Präsentation.

#### 4.2.1 Unregelmäßige Flächen

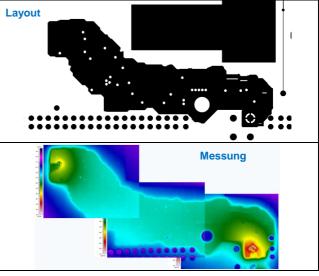

Bild 4 zeigt einen Ausschnitt aus einer der Testplatten mit einer besonders irregulären Form. Die Testleiterplatte ist 2-lagig. Als Besonderheit ist die *Wärmefalle* am rechten unteren Ende hervorzuheben. Die Hülsen und Bohrungen sind plattiert, haben aber keinen Kontakt zur Bottom-Fläche. Einen Vergleich in Zahlen gibt Tab. 1. Die Übereinstimmung liegt im 10% Bereich.

| Basismaterial                  | $T_{\text{max}}$ (°C) | U (mV) |

|--------------------------------|-----------------------|--------|

| Messung I=20 A, $T_U$ =21.4 °C |                       |        |

| FR4                            | ca. 52                | 66     |

| R1566 (mit Füllstoff)          | ca. 51                | 72.6   |

| Simulation                     |                       |        |

| FR4                            | 51                    | 60     |

| R1566                          | 49                    | 60     |

| R1566 ohne Wärmefal-           | 42                    | 54     |

| le                             |                       |        |

Tabelle 1 Vergleich Messung und Simulation zu Bild 4.

**Bild 4** Ausschnitt aus dem Layout einer Testleiterplatte, Thermogramm und Simulationsergebnis (s.a. Tabelle 1).

Die Wärmefalle trägt hier mit ca. 10 K zum Hotspot bei. Pin 2 ist in der Simulation ohne elektrischen Kontaktwiderstand und daher ohne erkennbare Zusatzheizung.

#### 4.2.2 Regelmäßige Leiterbahnen

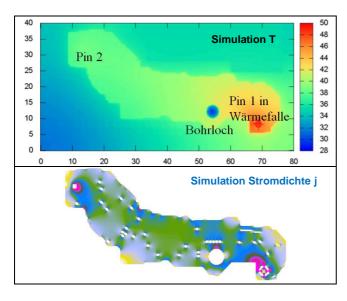

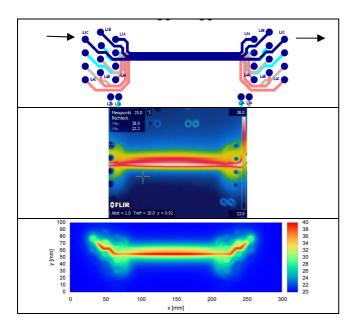

Als letztes stellen wir kurz das Ergebnis für ein 4-Lagen Board vor (Bild 5). Die (blaue) Bahn L1C auf Top wird mit 7 A belastet. Andere (unbenutzte) Anschlüsse führen auch in die Innenlagen, wo sich ähnliche Strukturen befinden. Die Leiterbahnbreite ist 3 mm, ihr Abstand 0.1 mm. Abgesehen vom Temperaturniveau, stimmen auch Details überein.

**Bild 5** Ausschnitt aus einem 4-Lagen Testboard mit einem bestromten Netz: Layout, Messung, Simulation.

#### 5 Schluss

Die Vergleiche von Thermographie und Simulation der von uns untersuchten Layouts zeigen eine gute Übereinstimmung der Temperaturerhöhung innerhalb von  $\pm 10\%$ . Dies konnte auch in aktuellen komplexeren Leiterplattenaufbauten mit mehr als nur einem Strompfad bestätigt werden. Wichtig ist, dass die Simulationsparameter, der Leiterplattenaufbau (Endkupferstärke) und die Messsituation zusammenpassen.

Aus der Zusammenschau von simulierter Temperatur und Stromdichte in den einzelnen Lagen kann man erkennen, wie Heizung und Kühlung in einer Lage korrespondieren. Änderungen im Layout liefern inkrementelle Verbesserungen oder Verschlechterungen, die die Simulation viel schneller offenbart als Musterbau und Thermographie. Wir können jetzt sehen, welchen Weg der Strom nimmt und daraus ein Layout gestalten, in dem möglichst alle Lagen und Querschnitte gut genutzt werden. Andererseits zeigt die Simulation auch schnell "Flüchtigkeitsfehler" beim Layouten, z.B. in Form von zu dünnen Leiterabschnitten. Nicht immer bedeutet eine lokal hohe Stromdichte auch eine lokal erhöhte Temperatur, aber die Summe von allen kleinen Heizungsinseln kann erkannt und hoffentlich korrigiert werden.

Der Wärmehaushalt einer Leiterplatte ist hochgradig nicht-lokal, so dass eindimensionale Abschätzungen mit Wärmewiderständen nur in Ausnahmefällen sinnvoll sind. Die Simulation zeigt dagegen sehr schön einerseits Sättigungseffekte und andererseits das Potential, das noch in einer Leiterplatte stecken kann. So manche Leiterplatte könnte kleiner gemacht werden, bei mancher könnte ein dünneres Basiskupfer ausreichen weil die zusätzliche Temperaturerhöhung vernachlässigbar ist.

Simulation liefert immer physikalische Einsichten und kann hier ökonomische Konsequenzen nach sich ziehen.

#### 6 Literatur

- [1] <u>www.ipc.org/TOC/IPC-2221A.pdf</u> und <u>www.fed.de</u> > Dokumentenshop

- [2] www.ipc.org: Standard for Determining Current Carrying Capacity in Printed Board Design und www.fed.de -> Dokumentenshop

- [3] Poschmann, H.: Neue Richtlinie: IPC-2152 Bestimmung der Strombelastbarkeit von Leiterplatten. PLUS 12 (2010), Heft 1 S. 60

- [4] Ihnenfeld, M.: "Deutsche Übersetzung der IPC-2152

Stromtragfähigkeit von Leiterplatten", PLUS 12 (2010), Heft 2 S. 322

- [5] Adam, J.: Neues von der Strombelastbarkeite von Leiterbahnen, DVS/GMM-Fachtagung "Elektronische Baugruppen Aufbau- und Fertigungstechnik". Fellbach (2004). GMM-Fachbericht 44 S. 117-123

- [6] www.adam-research.de/TRM.html