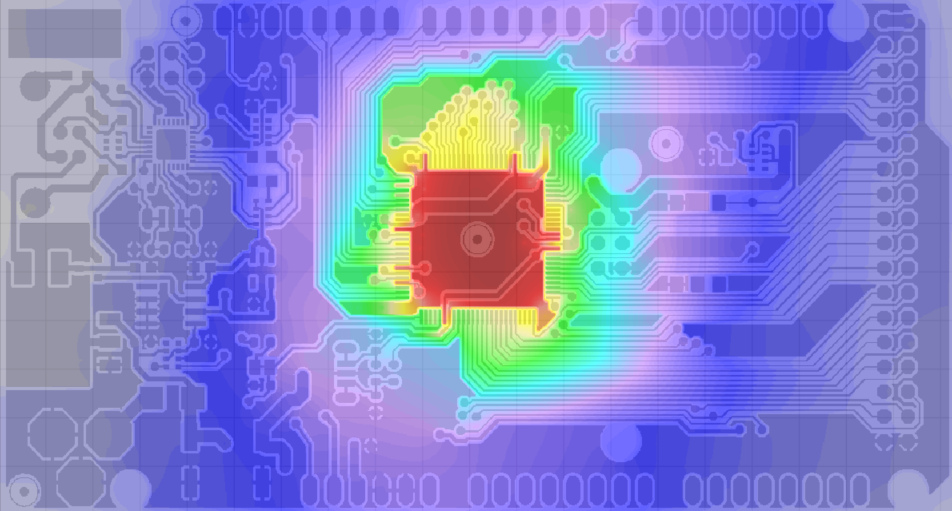

Bauteile und Ströme heizen die Leiterplatte (-Baugruppe) - aber wie heiß wird sie werden? Werden die Temperaturlimits eingehalten? Kein Datenblatt und keine Richtlinie wird es Ihnen sagen können.

Mit TRM (Thermal Risk Management) berechnen Sie die thermische Performance Ihrer Leiterplatte schon vor dem Labortest … und mit dem neuen TRM 3.7 ist es noch einfacher eine bessere Temperaturvorhersage zu erzeugen.

- Importieren Sie Ihre Gerber-, Bestückungs- , Bohrfiles und Netzliste oder setzen Sie Notwendiges manuell (s. FAQ)

· 3D-Leiterplattenmodell bis zu 50 Lagen

· Update: Einfacher Export und Import für ALTIUM User

· NEU: Einfacher Export und Import für EAGLE User

· Übersichtliche Bedienung (Oberfläche und Handbuch auf Deutsch und Englisch)

· Vorlagen- und Fileformate für Eingabeparameter

· Auch ohne CAD-Daten einsetzbar - für Technologen

· Keine FEM Kenntnisse erforderlich

· Genauigkeit durch Physik und Geometrie

· Heizung durch Bauteile und/oder Ströme

- Umgebungsbedingungen. Luftkühlung, Wärmesenken und Kühlkörper, Abstrahlung ins Vakuum, uvm

· Virtuelle Thermogramme aller Lagen und Prepregs in hoher Auflösung

· DC Potentialverteilung und Stromdichte in Netzen

· Stationär oder transient

· Temperaturabhängige Materialdaten

· Selbst- und Gegeninduktivität (Induktivitätsmatrix)

· Automatisch erzeugte Auswertetabellen

· Lizensierung über Ihren Server

· Kurze bis moderate Rechenzeit auf Laptop und PC

Fordern Sie eine kostenlose Testinstallation oder eine webdemo an.

Werfen Sie einen Blick in unser Lehrbuch.

YouTube: https://www.youtube.com/channel/UCFEwDzwApUYntiE__kJnJJQ